Lattice MachXO CPLD/FPGA VGA generator

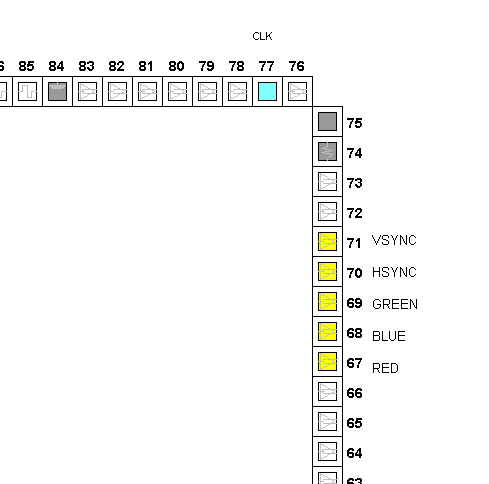

This FPGA Verilog design generates test pattern on a VGA monitor. The FPGA is connected as follows, CLK is 50 MHz:

Download: MachXO ispLEVER project package (verilog source).

The MachXO can be programmed using PLDTool and design debugged/programmed using JTAG Test. ispLEVER is available for free from Lattice Semiconductors.

Copyright(c)2008 SECONS Ltd.

Interested in easy to use VGA solution for embedded applications? Click here!

Interested in easy to use VGA solution for embedded applications? Click here!